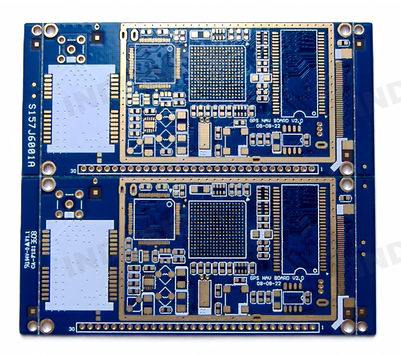

Leiterplattenfertigung

Spezialisiert auf die Fertigung von Präzisions-Leiterplatten (1-32 Lagen) mit engagiertem professionellem Support

Leiterplatte

Fähigkeiten

Kundenspezifische Leiterplattenlösungen

Schnelldurchlauf-PCB-Lösungen vom Prototyp bis zur Serienfertigung

Feature | Capability |

|---|---|

Quality Grade | Standard IPC 3 |

Number of Layers | 1 - 32layers |

Build Time | 1 - 5 days, 1 - 2 weeks, or scheduled deliveries |

Material | FR - 4 Standard Tg 150°C |

FR4 - High Tg 170°C | |

FR4 - High - Tg 180°C | |

FR4 - Halogen - free | |

FR4 - Halogen - free & High - Tg | |

Board Size | Min 6*6mm | Max 600*700mm |

Board size tolerance | ±0.1mm - ±0.3mm |

Board Thickness | 0.4mm - 3.2mm |

Board Thickness Tolerance | ±0.1mm - ±10% |

Copper Weight | 0.5oz - 6.0oz |

Inner Layer Copper Weight | 0.5oz - 2.0oz |

Copper Thickness Tolerance | '+0μm +20μm |

Min Tracing/Spacing | 3mil/3mil |

Solder Mask Color | Green, White, Blue, Black, Red, Yellow |

Silkscreen Color | White, Blue, Black, Red, Yellow |

Surface Finish | HASL - Hot Air Solder Leveling |

Lead Free HASL - RoHS | |

ENIG - Electroless Nickle/Immersion Gold | |

ENEPIG - Electroless Nickel Electroless Palladium Immersion Gold | |

Immersion Silver | |

Immersion Tin | |

OSP - Organic Solderability Preservatives | |

Min Annular Ring | 3mil |

Min Drilling Hole Diameter | 6mil, 4mil - laser drill |

Min Width of Cutout (NPTH) | 0.8mm |

NPTH Hole Size Tolerance | ±.002" (±0.05mm) |

Min Width of Slot Hole (PTH) | 0.6mm |

PTH Hole Size Tolerance | ±.003" (±0.08mm) - ±4mil |

Surface/Hole Plating Thickness | 20μm - 30μm |

SM Tolerance (LPI) | .003" (0.075mm) |

Aspect Ratio | 1.10 (hole size: board thickness) |

Test | 10V - 250V, flying probe or testing fixture |

Impedance tolerance | ±5% - ±10% |

SMD Pitch | 0.2mm(8mil) |

BGA Pitch | 0.2mm(8mil) |

Chamfer of Gold Fingers | 20, 30, 45, 60 |

Other Techniques | Gold fingers |

Blind and Buried Holes | |

Peelable solder mask | |

Edge plating | |

Carbon Mask | |

Kapton tape | |

Countersink/Counterbore hole | |

Half - cut/Castellated hole | |

Press fit hole | |

Via tented/covered with resin | |

Via plugged/filled with resin | |

Via in pad | |

Electrical Test |

Gerber-Dateien

-

Beachten Sie, dass Gerber-Dateien im RS-274x-Format vorliegen müssen.

-

Die Bohrdatei (pcbname.TXT) sollte im Excellon-Format vorliegen und die Daten zu Bohrlochgröße und -position enthalten.

-

Neben den Gerber-Dateien für die Produktion akzeptieren wir auch PCB-Dateien, die mit Eagle, Altium Designer oder PADS erstellt wurden.

-

Bitte hinterlassen Sie im Bestellprozess einen Kommentar zu Ihren Sonderwünschen.

-

Oberschicht:

-

Lötstoppmaske oben:

-

Seidentop:

-

NC Drill:

-

pcbname.GTL

-

pcbname.GTS

-

pcbname.GT

-

pcbname.TXT

-

Unterste Schicht:

-

Lötstoppmaske unten:

-

Seidenboden:

-

Mechanische Schicht:

-

pcbname.GBL

-

pcbname.GBS

-

pcbname.GBO

-

pcbname.GML

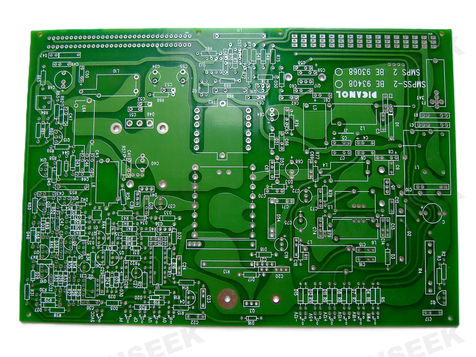

Leiterplatte

FLIESSEN

_edited_edited_edited_edited_.jpg)